最适合的器件

与TTL和ECL(双极)相比,CMOS器件更高的速度导致了更高的击穿电流,因此它在RFI和辐射方面的表现通常更差。当逻辑门的输出改变状态时,流过的大电流使杂散电容放电,这将产生可被耦合到下一个门和电路的其它部分的噪声电压。这个噪声像振铃,在门的输出端添加一个小电阻可以减弱振铃。

电容负载可比电阻负载吸引更多电流。运算放大器输出端的大电容负载可以造成剧烈的振铃,就像在数字门一样。简单的解释是:放大器的输出阻抗和负载电容形成了一个极点,造成运算放大器在频率响应的高Q值或者峰值。这可降低相位裕度并产生振荡。

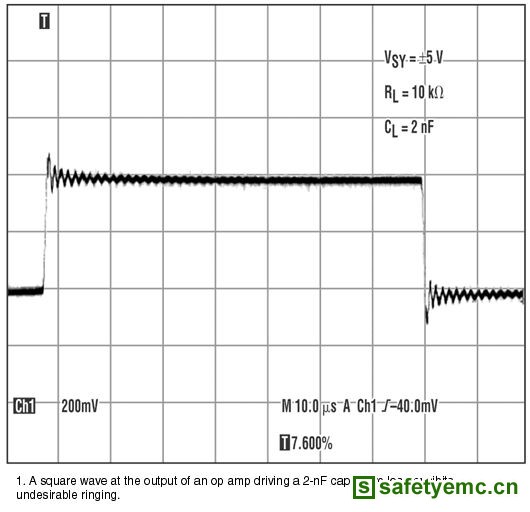

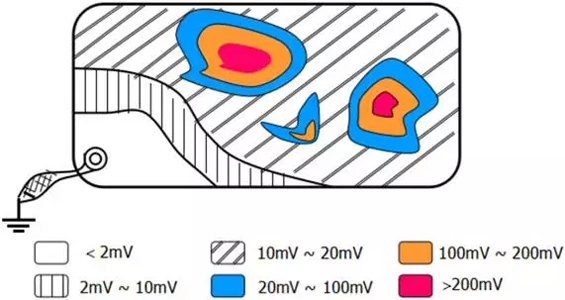

图1是运算放大器带2nF电容负载时的方波输出,信号里具有清晰可见的振铃

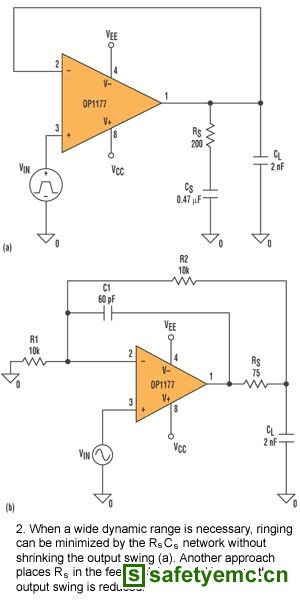

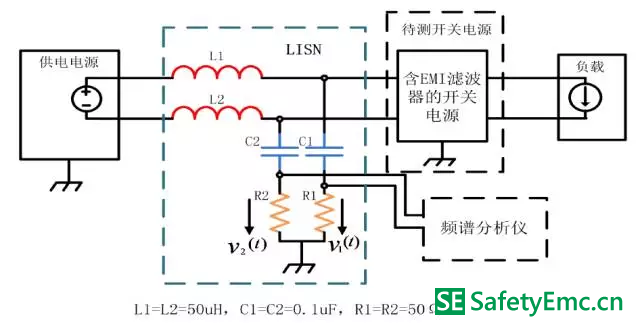

有两种方法可以消除振铃。第一个电路更适合需要宽动态范围的应用(图2a)。增加的RC网络(RS和CS)并不能减少输出摆动。这个实现被推荐用于非轨到轨输出运算放大器。

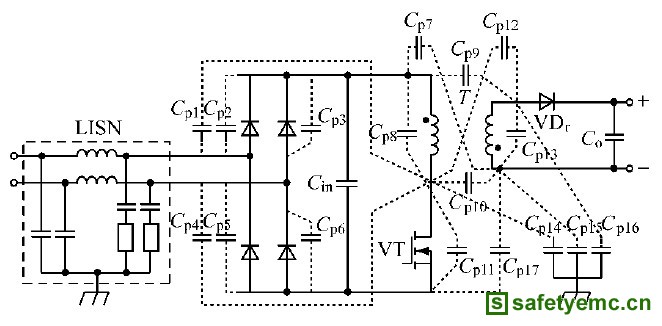

图片2b给出另外一种办法。除了能处理大电容负载以外,这个电路还能在运算放大器的输出端过滤噪声。可是,由于在反馈环路中插入了阻抗(RS),输出摆动减少了。因此,这个方法更适合用于轨到轨输出运算放大器。

苏公网安备32050802011615号

苏公网安备32050802011615号