在千兆赫的速度下撷取输出讯号

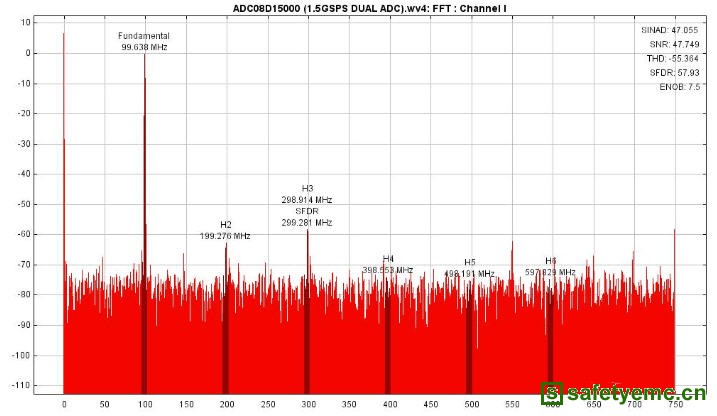

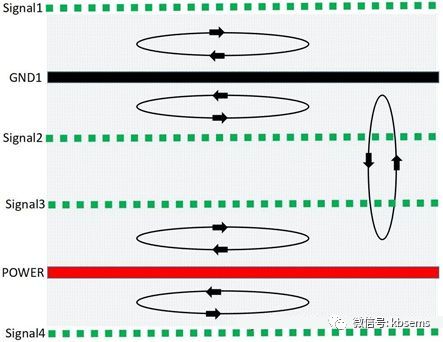

大家普遍都知道技术先进的FPGA可以处理的数据率最高达800Mbps,若超过了这个范围,就需要像8B10B这样的编码方式来保证良好的BER(误码率)。在处理这样高数据传输率时,电路板布局和设计是非常重要的一环,例如ADC输出和FPGA输入间的走线 度必须完全匹配;失配将引起时序偏差因而引发位错误。新型千兆赫ADC组件有一个DCLK(数据输出频率),可将输出至FPGA或ASIC的数据数据闩锁住,这个DCLK能在SDR(单数据传输率)或DDR(双数据传输率)模式下运作以协助进行撷取数据。

度必须完全匹配;失配将引起时序偏差因而引发位错误。新型千兆赫ADC组件有一个DCLK(数据输出频率),可将输出至FPGA或ASIC的数据数据闩锁住,这个DCLK能在SDR(单数据传输率)或DDR(双数据传输率)模式下运作以协助进行撷取数据。

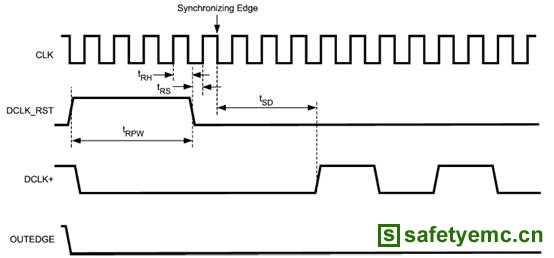

在新型千兆赫ADC组件可达到的、非常高的速度下,DCLK长度和数据在线的微小差别就代表着数据撷取成功和错误之间的区别。因此,新型千兆赫ADC组件提供了一个OutEdge接脚在DCLK边缘上撷取数据,此接脚最适用于应用电路和布局。

多个ADC同步

ADC常透过交叉存取来增加取样频率,并超过单独装置所能应用的范围,一个经常面对的挑战是使ADC输出数据流同步。这个系统开发者必须确切知道在ADC输出下的哪些数字文字组与系统前端的讯号取样符合。

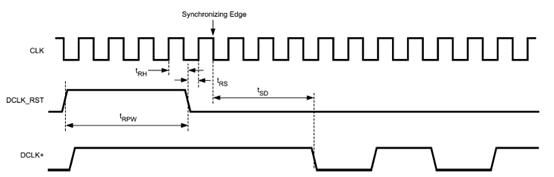

为了简化交叉存取,ADC08DXXX系列具有将输入到DCLK输出的取样频率精确重置能力,就像由客户供应的DCL_RST 脉波一样。这就允许在同一个系统中的多个ADC,根据它们共享的、用于取样的CLK来促使DCLK(和数据)输出转换同步。图3显示了在DDR模式下DCLK重置频率。

图3:在DDR模式下DCLK重置频率

由于在FR04 PCB材料上,讯号以15 cm/ns的速度进行传播,因此如果这些ADC没有被很密集的布置在一起,图3中的设置时间将很难达到。

在这种情况下,输入频率能够有短时间的暂停(< 50 ns),因此在DCKL_Res确定的过程中保持AC耦合(注意推荐使用针对输入频率的耦合)。AC-耦合电容器的持续时间为50K((内部偏置电阻器)x 4.7nF (外部AC-耦合电阻器) = 235 μs,因此不必担心频率在小于50ns的暂停下会明显地de-bias AC耦合电容。

在频率停止的过程中,DCLK Res可以同步确定。

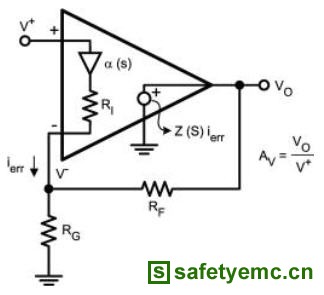

图4中展示了用在DCLK重置的简化框图。

图4:适用于多个ADC同步的框图DCLK 复位

结语

目前在市场上已推出了与Xilinx Virtex-4 FPGA合并的开发平台,这个平台利用功能模块来设计,其中包括ADC和FPGA、ADC和FPGA之间互联的LVDS、连接于使用平衡转换器和差动放大器的ADC的模拟输入网络、使用PLL和VCO的电路板上系统频率、完整的供电设计及温度控制电路。这些模块中的每一项都可以被设计者重复使用以便大幅加快研发进度﹗

此FPGA有数千个尚未使用的闸 、DSP和内存,设计师可针对适当的韧体开发对它们进行编程。一个并行总线扩展端口可轻易地连接到FPGA I/O,此端口带有一个高速逻辑分析仪的接头来辅助进行设计调整。上述的一切都允许设计者在不需要选择和测试每个组件和使用外部测试设备的情况下,同时开发硬件及FPGA逻辑设计。

此开发平台仅仅要求一个电源和USB连接,便可从任何输入讯号中选择和储存数据,并能将测试结果上载到个人计算机中进行分析。

作者简介:Nicholas Gray 任职于美国国家半导体公司数据转换系统部应用工程师,电子邮件:nicholas.gray@nsc.com

苏公网安备32050802011615号

苏公网安备32050802011615号