对于高频系统来说,电磁干扰是个不小的危害,噪声具有频谱宽、隐蔽性强、难于消除等特点,因此将噪声抑制到最小对提高系统性能指标是必要的。对于抑制噪声、减小EMI,可以通过改进电源方案、降低电源噪声、优化时钟方案、正确产生逻辑信号,以及设计接口电路和信号线连接部分。本文将阐述如何通过上述方案减小高频系统控制电路产生的噪声以提高系统性能。

对于实现10纳秒触发控制电路这一基本功能并不是一件难事,但是对于某些领域,会有一些特殊的要求,要想完全达到指标,对电磁兼容性有很高要求。本文提出的设计应用于对高频电路的控制,可实现对系统无射频干扰,传输距离可达到30米,满足TTL电平要求,最高时钟频率为50MHz。

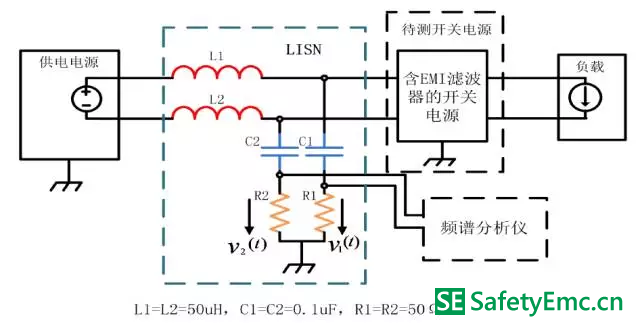

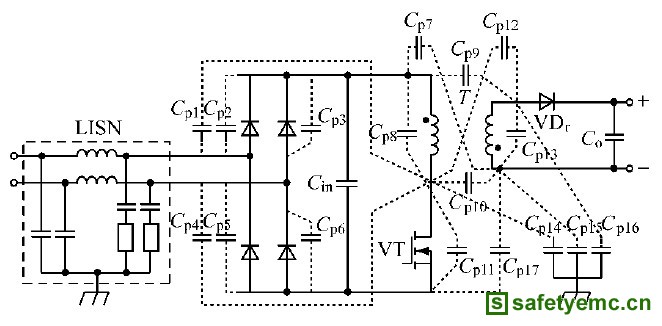

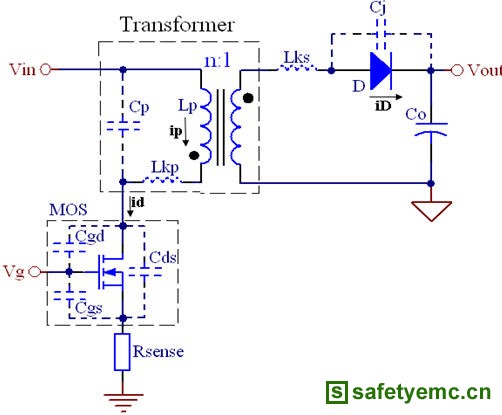

整个电路设计主要分为四部分:电源部分设计(包括底层设计)、时钟部分设计、逻辑部分设计和接口部分设计。对于减小系统噪声,电源的管理是首要的。首先采用高性能DC-DC进行电能的转换,把有纹波输出的直流电源隔离。控制电路中并不是单电源供电的,对于缓冲电路是采用5V供电,对于可编程器件采用3.3V和1.5V供电,因此还需要两个LDO对电压进行变换。

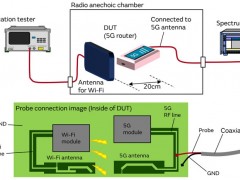

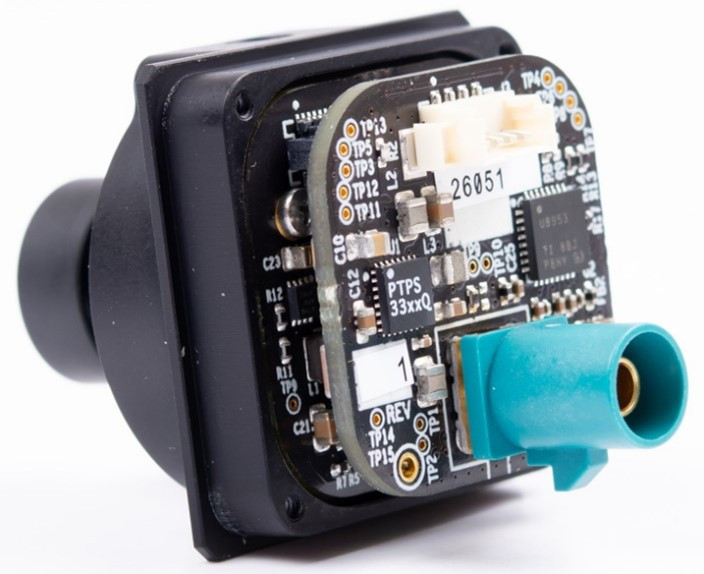

对于外部时钟部分,电路中采用了精度小于30ppm的3.3V晶振,给可编程器件提供时钟源。由于可编程逻辑器件内置锁相环,可以保持与外部时钟的同步,同时还可满足倍频需要,可编程逻辑器件还内置全局时钟总线,可满足逻辑的同步建立。为了驱动外部TTL设备,控制系统采用了可编程逻辑器件和高速CMOS器件进行缓冲,为了实现长距离传输,还需对输出信号进行终端匹配。接口部分指的是接插件,接插件具有较大的引线电感,很容易造成信号传输线的阻抗不匹配,因此需要做好屏蔽才能减少EMI问题。

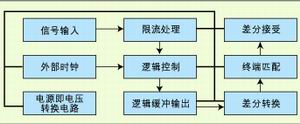

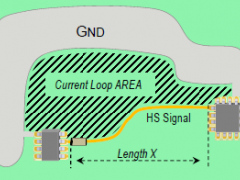

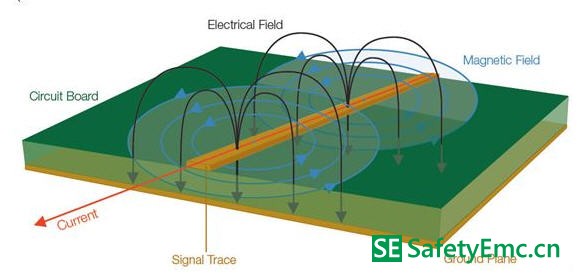

为了提高整体性能和增强抗ESD能力,电路采用四层PCB板设计。四层板的排列为:第一层为元件层和重要信号布线层,第二层为地层,第三层为电源层,第四层为一般信号布线层。第一层紧邻地层,可对信号回路提供最好的耦合,因此应布最重要的信号线,同时为了减小引线电感,顶层器件全部选用表贴器件。第二层为地平面,对地层信号提供最好的耦合回路,同时对电源层提供一定的去耦。第三层电源层只是直流电源走线,为简化设计,并未布置成电源面,对于没有电源线的空白区域,可以布置一些不是很重要的信号线,而且这些信号线要距离电源线较远,不能对电源造成串扰。第四层为信号线层,对于缓冲器后面的线,由于加了终端匹配,上升沿变缓,因此不容易超过电长走线长度,基本在第四层传到控制输出端口。控制整体框图如图1所示。

电路的电源及接地部分设计

苏公网安备32050802011615号

苏公网安备32050802011615号