ESD通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD的影响。具体到I/O,就是与PAD相连的输出驱动和输入接收器。根据对ESD低阻放电通路的要求,上面六条通路必须保证在ESD发生时,形成与保护电路并行的低阻通路,旁路ESD电流,且能立即有效地钳位保护电路电压。而在这两部分正常工作时,不影响电路的正常工作。

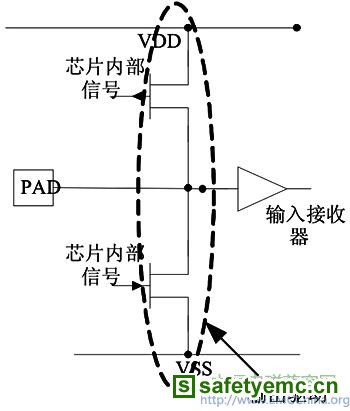

图2 典型的I/O电路示意图

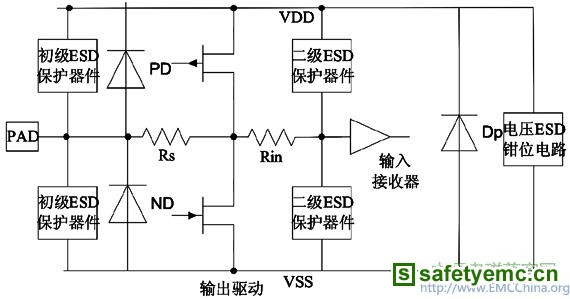

图3是加入ESD电流通路的I/O电路,在图3所列的所有器件中,HBM模式下 输出驱动上的NMOS管是最容易受损坏的。因此下面会对输出驱动中NMOS管的ESD低阻旁路给出比较详细的介绍。

图3 加入ESD电流通路的I/O电路,二极管ND是NMOS漏极与P型衬底形成的寄生二级管,二极管PD是PMOS漏极与N阱形成的寄生二级管,VDD与VSS之间的二极管Dp是N阱与P型衬底形成的寄生二级管。电阻Rs和Rin用于进一步降低被保护器件上的ESD电压。

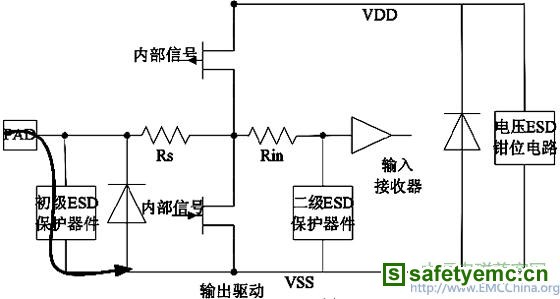

● PS模式下PAD、VSS之间的ESD低阻旁路

每一个I/O引脚电路中都应建立一个PAD到VSS的ESD保护电路(图4)。

图4 PAD对VSS反向ESD放电时的电流通路

常用的ESD保护器件有电阻、二极管、双极性晶体管、MOS管、可控硅(SCR)等。由于MOS管与CMOS工艺兼容性好,我们常采用MOS管构造保护电路。

CMOS 工艺条件下的NMOS管有一个横向寄生n-p-n(源极-p型衬底–漏极)晶体管,如图5(a)所示。

这个寄生的晶体管开启时能吸收大量的电流。利用这一现象可在较小面积内设计出较高ESD耐压值的保护电路,其中最典型的器件结构就是栅极接地NMOS(GGNMOS,Gate Grounded NMOS)。

在正常工作情况下,NMOS横向晶体管不会导通。当ESD发生时,漏极和衬底的耗尽区将发生雪崩,并伴随着电子空穴对的产生。一部分产生的空穴被源极吸收,其余的流过衬底。由于衬底电阻Rsub的存在,使衬底电压提高。当衬底和源之间的PN结正偏时,电子就从源发射进入衬底。这些电子在源漏之间的电场的作用下,被加速,产生电子、空穴的碰撞电离,从而形成更多的电子空穴对,使流过n-p-n晶体管的电流不断增加,最终使NMOS晶体管发生二次击穿,此时的击穿不再可逆,则NMOS管损坏。

苏公网安备32050802011615号

苏公网安备32050802011615号