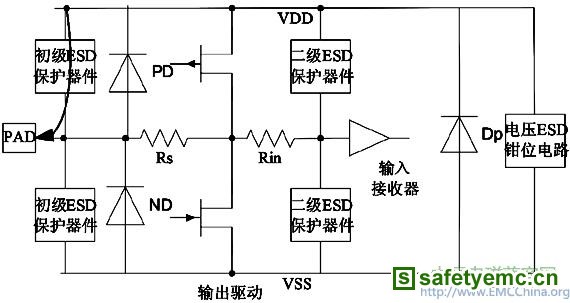

● PD模式下PAD,VDD之间ESD低阻旁路

在ESD过程中,如果PAD对VDD正向放电, 放电通路由N阱和每一个与PAD相连PMOS的漏极产生的寄生二极管组成。此时二极管正向导通,有很高ESD防护能力,PAD对VDD的正向放电可以很容易的分布到芯片各个管脚。

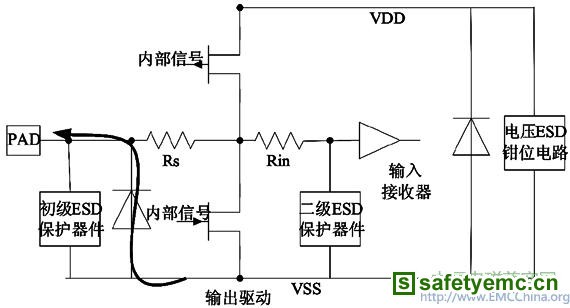

图9 PAD对VSS反向ESD放电时的电流通路

● ND模式下VDD,PAD之间ESD低阻旁路

在ESD过程中,如果PAD对VDD负向放电,放电通路如图10。PAD对VDD负向放电通路由PMOS横向寄生晶体管组成。电路原理和结构与PS模式下PAD到VSS的电路类似。

图10 PAD对VDD反向放电电流通路

●VDD,VSS之间ESD低阻旁路

VDD,VSS的PAD上也可能发生ESD事件,因此也需要有ESD保护。

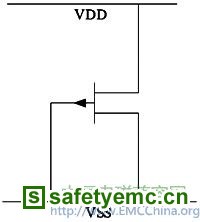

在ESD过程中,如果VDD对VSS正向放电,基本的VDD到VSS的保护电路结构是在VDD和VSS之间加一个大尺寸的GGNMOS(如图11)。为了提高VDD到VSS之间保护电路的效率,减小电源线间寄生电阻电容对其ESD保护性能的影响,可将这个保护电路复制多份,分布到芯片中去。

图11 VDD到VSS基本ESD电路保护结构

在ESD过程中,如果VDD对VSS反向放电,ESD电流通过P衬底和N阱形成的二极管被旁路掉,此时这个寄生二极管正向导通,所以它的ESD保护能力强。

● PAD,PAD之间ESD低阻旁路

在PAD 到PAD的电流通路中,ESD电流经输入端的ESD保护器件流入电源线,再通过电源线流经各个输出端的ESD保护器件到地。

5 综述

ESD保护电路不是单一芯片引脚的问题,它要从整个芯片全盘考虑。芯片里每一个I/O电路中都需要建立相应ESD保护电路,ESD保护电路在版图中要画在PAD旁。VDD到VSS之间也需要ESD保护电路,VDD到VSS之间的ESD保护电路在芯片中要能多次引用。每一个有输入接收端的I/O电路上应加二级ESD保护,二级ESD保护电路在版图中要尽量靠近输入接收端。电源线用于吸收ESD电流,在版图中尽量画宽,减小电源线上的电阻。

参考文献

[1]. JESD22-A114D,

[2]. Ajith Amerasekera, Charvaka Duvvury,“ESD in Silicon Integrated Circuits, 2nd Edition/On”,John Wiley & Sons, Ltd, 2002

[3].SanjayDabral and Timothy Maloney,“Basic ESD and I/O design”,John Wiley & Sons, Ltd,1998

[4]. MOS集成电路的ESD模型和测试方法探讨

苏公网安备32050802011615号

苏公网安备32050802011615号