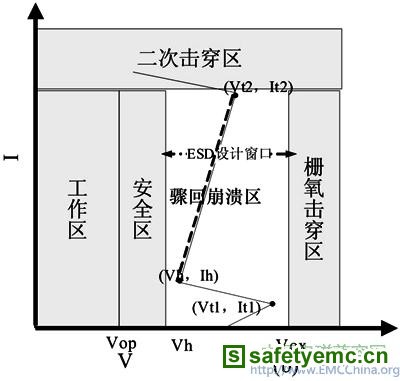

图5(b)展示了这一过程的I-V特性,其中(Vt1,It1)为衬底和源之间的PN结正偏,横向晶体管开启时的电压电流,(Vh,Ih)为NMOS横向晶体管的钳位电压和电流,(Vt2,It2)是NMOS横向晶体管发生二次击穿时的电压和电流。NMOS管正常工作的区域在Vop之内。为了防止如噪音等外界影响,使NMOS在正常工作区域触发,Vop与Vh之间需要一个安全区。Vox是NMOS管的栅氧击穿电压。如果ESD保护器件的电压设计在安全区与栅氧击穿区之间,电流设计在It2以内,ESD保护器件就能在不损伤管子也不影响工作电路的情况下完成对电路的保护。

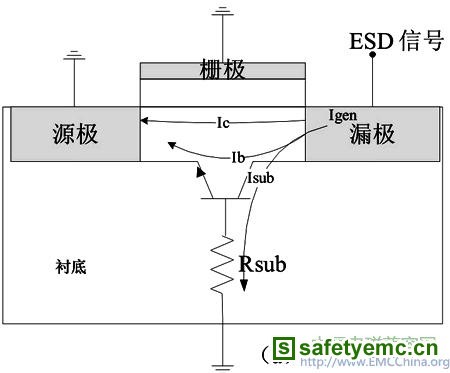

图5 (a)NMOS管有一个横向寄生n-p-n(源极-p型衬底-漏极)晶体管。Rsub为衬底电阻(b)ESD设计窗口。

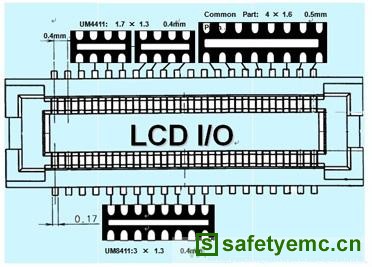

我们可以通过ESD钳制电路的HBM耐压值来推断ESD钳制电路器件的大概宽度。如果GGNMOS可通的最大电流密度是10mA/μm, 则要达到2kV HBM耐压值,这个ESD钳制电路要经受1.33A的电流(图1),NMOS的宽度至少是133μm。为了在较小的面积内画出大尺寸的NMOS管子,在版图中我们采用常把它画成手指型(finger-type),把NMOS管中的单一“手指”作为一个单元,然后多次引用这个单元。画版图时应严格遵循I/O ESD的设计规则。

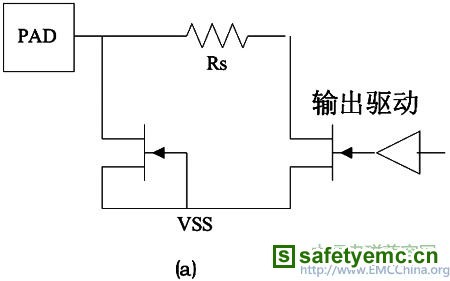

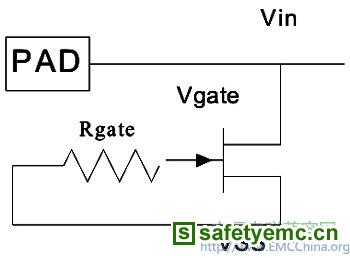

为了进一步降低输出驱动上NMOS在ESD时两端的电压,可在ESD保护器件与GGNMOS之间加一个电阻(图6)。这个电阻不能影响工作信号,因此不能太大。画版图时可采用多晶硅(poly)电阻。

图6 (a)PAD到VSS电流通路的等效电路图(b)ESD发生时的I-V特性图,电阻Rs会让ODESD耐压值有一个Ir2OD*RS的偏移。

苏公网安备32050802011615号

苏公网安备32050802011615号