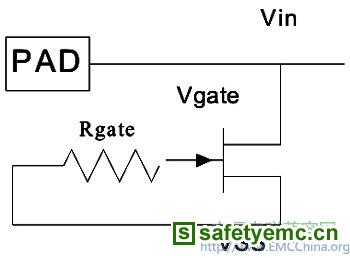

在ESD发生时,不一定每一个NMOS“手指”会一齐导通,这样ESD保护电路的有效耐压值就由开始导通的几个NMOS“手指”决定。为了避免这种情况,提高ESD器件防护能力,可在NMOS栅极和地之间加一个电阻Rgate(图7)。

(a)

(b)

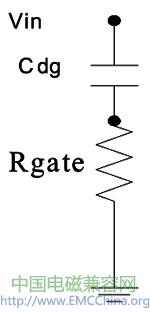

图7 (a)在输出驱动NMOS管栅地间加上电阻(b)栅地加电阻后,ESD时的等效电路图Cdg为NMOS管栅漏间的寄生电容。

由于栅漏间寄生电容的存在,ESD瞬态正电压加在PAD上时,图7中NMOS上的栅极也会耦合一个瞬态正电压,因此NMOS上的每一个“手指”会一齐导通, 不用到达Vt1就能进入寄生横向晶体管骤回崩溃区(snapback region)。栅极电压由Rgate放电到地。这个瞬态电压持续的时间由栅漏寄生电容和栅地电阻组成的RC时间常数决定。栅地电阻必须足够大,保证在电路正常工作时这个栅极耦合NMOS管是关闭的。

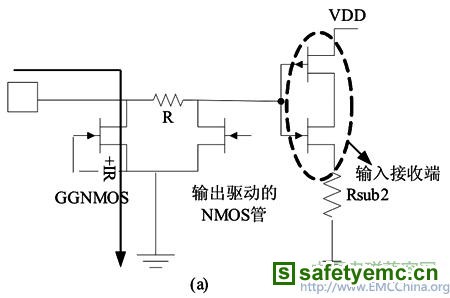

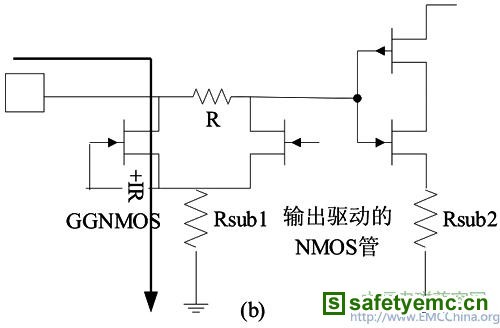

只采用初级ESD保护,在大ESD电流时,电路内部的管子还是有可能被击穿。如图8所示,GGNMOS导通,理想状况下(图8a),衬底和金属连线上都没有电阻,吸收大部分ESD电流。实际情况是(图8b),GGNMOS导通,由于ESD电流很大,衬底和金属连线上电阻都不能忽略,此时GGNMOS并不能钳位住输入接收端栅电压,因为让输入接收端栅氧化硅层的电压达到击穿电压的是GGNMOS与输入接收端衬底间的IR压降。为避免这种情况,可在输入接收端附近加一个小尺寸GGNMOS进行二级ESD保护(图8c),用它来钳位输入接收端栅电压。在画版图时,必须注意将 二级ESD保护电路紧靠输入接收端,以减小输入接收端与二级ESD保护电路之间衬底及其连线的电阻。

图8(a)理想状况下的电流通路(b)长距离产生的寄生电阻使输入接收中的栅氧被击穿(c)解决方法

● NS模式下VSS,PAD之间ESD低阻旁路

在ESD过程中,如果PAD对VSS负向放电,放电通路由p型衬底和每一个与PAD相连NMOS的漏极产生的寄生二极管组成,如图9所示。此时二极管正向导通,因为二极管正向导通电压小,导通电阻小,有很高ESD防护能力,PAD对VSS的负向放电可以很容易的分布到芯片各个管脚。

苏公网安备32050802011615号

苏公网安备32050802011615号