展频系统中其余组件的时钟跟随

时钟展频能够很容易的整合至系统的时钟电路设计中,并有效降低系统电磁波峰值的产生。但在另一方面,若电路中的展频时钟电路之后,设计了其它的锁相回路,并利用展频的时钟来做为这些锁相回路的信号来源,在设计上就必须特别注意了。因为展频对系统的时钟进行不断的调变,下游的锁相回路组件必须能够快速的反应,追随这些频率变动,此时若是锁相回路的频宽不足,就容易产生时钟追踪的歪斜,造成系统时钟抖动的增加。工程师们必须确定电路中所有的锁相回路组件都能够正确的追踪展频时钟频率的变动,若这些串接的锁相回路做为时钟电路缓冲器中的组成部分,可以采用像是Spread?Aware这一类专为展频电路所设计并测试合格的时钟组件。

结 语

目前的时钟电路运作频率极高,容易产生电磁波噪声,当电磁波的强度超过一定的程度时,将产生不可预期的影响,不可不注意预防。目前已有许多以机械结构或是改变电路布局方式的电磁波干扰防治解决方案,但是这些解决方案都耗时费事,若能在电路设计上的小细节多加留意,就可以有效的预防电磁波噪声的产生。

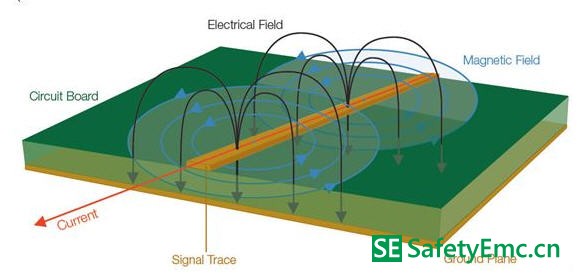

时钟信号若是没有妥善的被终结,或是时钟组件具有快速的瞬时特性,都会产生大量的电磁波噪声。若要控制电磁波噪声的产生,必须考虑下列几项原则:

●妥善的终结所有的时钟信号

●尽量采用波缘上升速度较低的时钟缓冲组件

●在信号线路中采用滤波电容器

●在高速的电路中采用展频时钟组件

只要在电路设计上遵守这些简单的规则,就可以以最低的成本,有效的控制电磁波噪声的产生,提高产品的竞争力。

苏公网安备32050802011615号

苏公网安备32050802011615号